7 muutettua tiedostoa jossa 16 lisäystä ja 26 poistoa

+ 14

- 2

Documentation/docs/Build-instructions/verilog.md

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

BIN

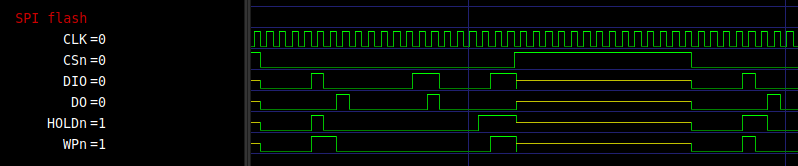

Documentation/docs/images/gtkwave.png

BIN

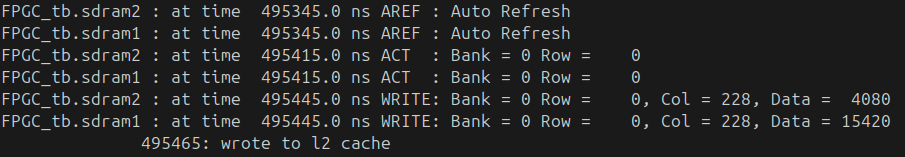

Documentation/docs/images/vvp.png

+ 0

- 8

SublimeText3/b32p.sublime-build

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

+ 0

- 6

SublimeText3/python3.sublime-build

|

||

|

||

|

||

|

||

|

||

|

||

|

||

+ 0

- 8

SublimeText3/verilog.sublime-build

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

+ 2

- 2

Verilog/testbench/FPGC_tb.v

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||

|

||